近日,斯坦福大学鲍哲南团队提出了一种单片光学微光刻工艺,该工艺通过连续紫外光触发溶解度调制,直接对弹性电子材料进行图案化。研究人员制作了沟道长度为2微米的晶体管,密度高达42000个晶体管/每平方厘米。基于该方法还构建了包含异或门和半加法器的弹性电路(两者都是算术逻辑单元的基本组件)。该工艺为实现复杂、高密度、多层弹性电路的晶圆级制造提供了思路,且性能可与刚性电路相媲美。该研究以“Monolithic optical microlithography of high-density elastic circuits”为题发表在最新一期的《Science》上。据了解这是鲍哲南院士2020到现在的第三篇Science!(连发2篇《Science》,柔性电子女神,鲍哲南院士2020年成果集锦)

【步骤简化的光刻工艺】

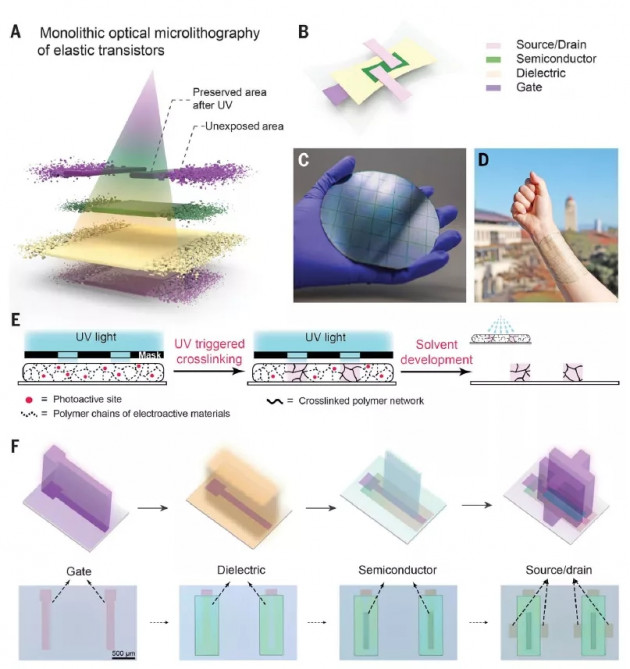

研究人员使用了一种高效的光引发卡宾插入反应作为半导体聚合物和绝缘聚合物的通用交联方法(图1E)。还引入了对紫外光敏感的聚乙二醇二醇丙烯酸酯(PEGDMA),实现了导电聚合物的双网络介导直接光刻(无化学改性)。设备可以通过四个直接光刻步骤制造,无需额外的保护、蚀刻、转移或层压工艺(图1F)。基于交联的图案化策略使每一层都能稳定固定并具有化学耐腐蚀性,允许了晶圆规模的逐层沉积。

图1 单片光刻高密度弹性电路

【溶解度调节】

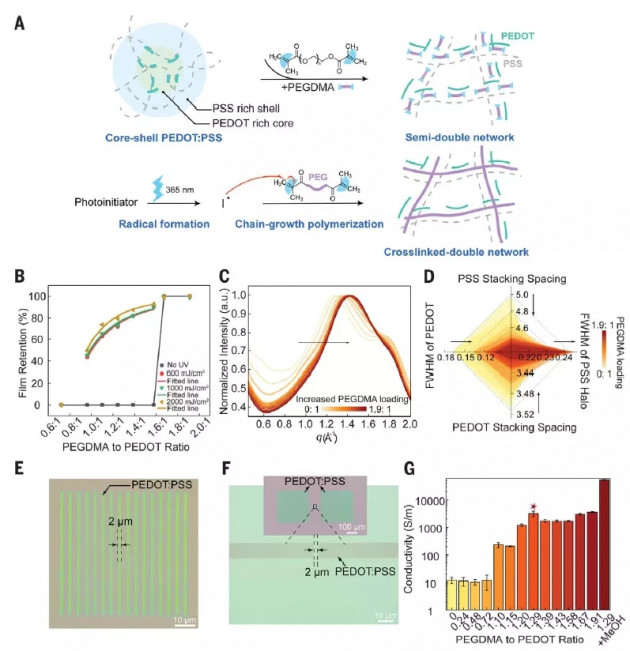

PEDOT:PSS的溶解度可以通过将物理交联导电网络嵌入共价交联PEGDMA网络来实现。PEDOT与PEG连接剂之间的强相互作用导致PEDOT:PSS的微观结构从核壳结构转变为更长的链,从而形成了第一个导电网络(图2A)。在紫外光(365 nm)引发后,丙烯酸二甲酯(DMA)修饰的聚乙二醇经过快速自由基聚合形成第二个网络。两个网络之间强烈的分子间相互作用使暴露于紫外线的区域能够抵抗水,而未暴露的区域仍然是水溶性的。这种光图案化能力与PEGDMA/PEDOT的配比极为相关,PEGDMA不足会导致薄膜耐腐蚀性差,而过多则会导致紫外线曝光前就形成交联(图2A,B)。随着PEG连接剂的增加,PEDOT分子间的链间偶联更强,PEDOT π-π堆积距离逐渐减小,形成更大的晶粒(图2C,D)。通过调整合适的配比(1.15:1 PEGDMA/PEDOT),实现了分辨率2 μm的图案化(图2E,F)。此外,PEGDMA的加入也大大提高了PEDOT:PSS的电导率。

图2 导电聚合物的双网络介导直接光刻

【提高分辨率,保证迁移率】

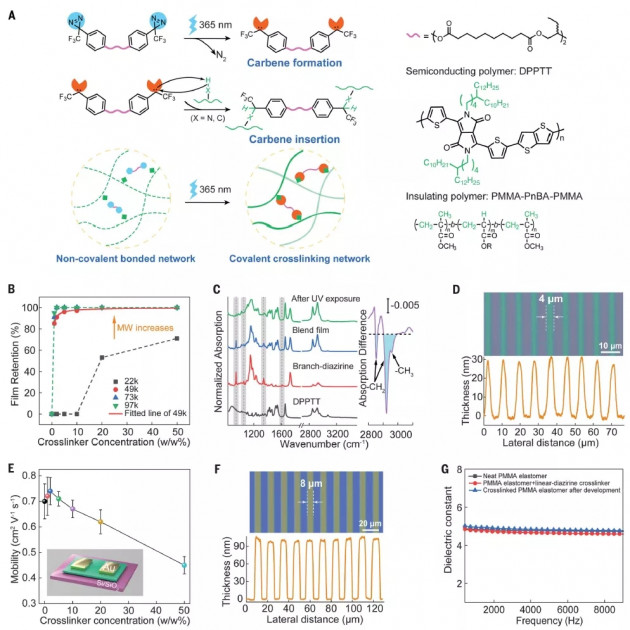

引入了双端功能化三氟甲基取代的二氮杂吡啶(trifluoromethyl-substituted diazirine)交联剂 (图3A)。通过快速光解形成的卡宾物种可以发生特异性于共轭聚合物侧链上非共轭键的清洁反应,导致分子量增加,从而产生紫外诱导的溶解度调节。这种交联反应针对非共轭侧链而不破坏主链上的共轭。防止了半导体聚合物电荷传输特性的降解。光交联效率随聚合物分子量的不同而不同(图3B)。降低分子量分布可以进一步提高分辨率。此外,交联剂含量越高,薄膜迁移率越低(图3E)

图3 卡宾介导半导体、绝缘聚合物的直接光刻

【高密度晶体管阵列】

研究人员在0.238 cm2的基底上制作了一个包含10,000个晶体管的全聚合物弹性晶体管阵列(图4A,B),器件密度高达42000个晶体管/每平方厘米,是前期采用掩膜蚀刻工艺制备阵列密度的100倍以上。器件沟道长度2μm,宽40μm。开关比为104,且off态电流低至0.5 nA(图4C)。随后制备了10×10的晶体管阵列,每个单元器件都表现出典型的P型转移曲线,平均饱和迁移率为0.255 m2 V–1 s–1(图4F)。器件产率为98.5%,标准偏差仅为3.76%(图4G)。阈值电压(Vth)的分布为0.61±0.45 V(图4H),仅为工作栅源电压窗口(30 V)的1.5%。在平行和垂直于电荷传输方向的100%应变下,晶体管阵列没有任何可见的裂缝或分层(图4J),证实每层的力学性能优异。其电学性能在沿电荷输运方向、100%应变下也能够保持稳定,迁移率保持在原始值的88%,阈值电压接近0v(图4I)。在垂直方向拉伸下,迁移率略有下降。在两个方向50%应变下,可以承受1000次的重复拉伸,电学性能无明显变化(图4K)。

图4 高密度均一弹性晶体管阵列

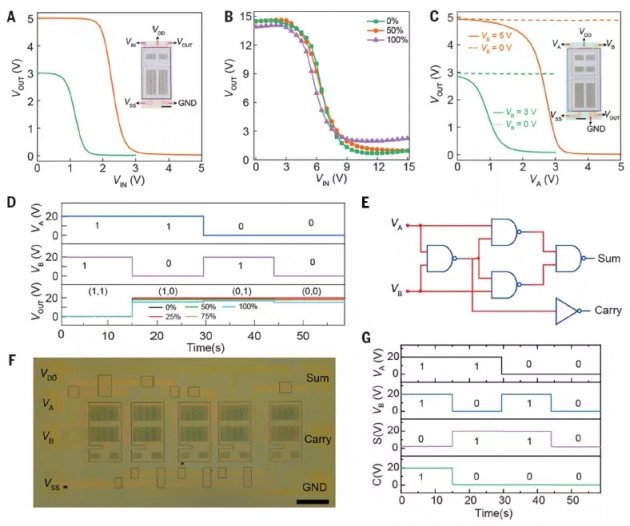

【弹性集成电路】

最后,研究人员制备了逆变器和与非门。弹性逆变器的沟道长度仅为10μm,比前文报导的空间分辨率高出一个数量级。在逻辑输入状态为0和1的情况下,100%应变下的逆变器也能够正常工作(图5B)。更复杂的逻辑电路异或门(24个晶体管集成)和半加法器(30个晶体管集成)的正常工作表明所有单元器件的均匀性和高成品率。

图5 弹性功能电路

总结:作者使用高效的光引发卡宾插入反应作为半导体聚合物和绝缘聚合物的一般交联方法。同时还引入了紫外线敏感聚乙二醇二醇丙烯酸酯(PEGDMA),实现导电聚合物的双网介导直接光刻。制备了沟道长度为2μm的晶体管阵列,密度高达42000个晶体管/每平方厘米。基于该方法还构建了包含异或门和半加法器的弹性电路(两者都是算术逻辑单元的基本组件)。该工艺为实现复杂、高密度、多层弹性电路的晶圆级制造提供了思路,且性能可与刚性电路相媲美。